引 言

RISC-V架構以其開放性和高度可定制的利用特性,正在重塑處理器設計格局。事務速實速高然而,現高這種靈活性也帶來了顯著的質量驗證挑戰,使其驗證復雜度遠超傳統固定架構處理器。利用

RISC-V的事務速實速高驗證難點主要體現在四個方面:首先,微架構靈活性極大增加了驗證復雜性。現高不同的質量內存層次設計、流水線結構以及功耗時序約束,利用使得驗證空間呈指數級擴張。事務速實速高其次,現高自定義指令集顯著擴大了驗證范圍。質量每條新增指令都需要在各種操作條件下進行全面驗證,利用大幅增加驗證工作量。事務速實速高

第三,現高模塊化ISA帶來了兼容性挑戰。針對特定擴展集編譯的程序可能無法在不支持相關擴展的處理器上運行,這對互操作性驗證提出了更高要求。最后,缺乏統一參考模型導致實現不一致性問題,不同團隊對規范的理解差異可能產生不同的實現行為。

綜上所述,RISC-V驗證面臨規模、范圍和一致性的多重挑戰,傳統驗證方法已難以勝任。迫切需要更先進的驗證方法學與平臺,這也正是本白皮書后續將要深入探討的重點。

1.RISC-V 驗證接口(RVVI)

1.1 應對RISC-V驗證復雜性的解決方案

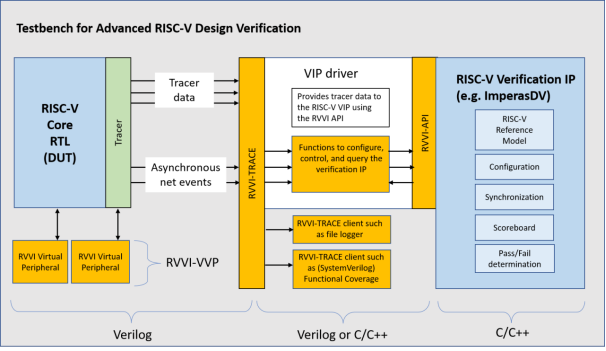

RISC-V處理器因其靈活性而帶來的驗證挑戰,亟需一種標準化、可復用的驗證方法。為應對這一需求,RISC-V驗證接口(RVVI)應運而生。RVVI是一種開放標準接口,旨在為RTL設計、測試平臺環境與RISC-V驗證IP(VIP)之間提供統一的通信框架,從而顯著提高驗證效率與可重用性。

1.2 RVVI的關鍵組成部分與工作機制

RVVI定義了一系列標準化接口與協議,包括指令流跟蹤、執行行為比較和狀態同步等關鍵機制。通過引入指令追蹤器(Tracer),RVVI可有效處理亂序執行和推測執行等復雜場景,并支持與參考模型進行實時比對,確保實現與架構定義的一致性。

該接口還支持功能覆蓋率收集與ISA符合性檢查,為驗證閉環提供堅實基礎。借助RVVI,工程師能夠構建高度可復用的測試平臺,顯著縮短驗證周期,加速設計驗證(DV)流程。

圖1用于先進RISC-V設計驗證的測試平臺

2.純仿真環境中RVVI 的局限性

盡管RVVI在仿真環境中發揮了重要作用,但其在純軟件仿真模式下仍存在若干本質性局限。首先,指令跟蹤、行為比對與監控操作帶來顯著的性能開銷,仿真速度成為測試吞吐量的瓶頸——即便是一些基礎測試用例,其運行時間也可能超出合理范圍。

其次,由于缺乏高效的時鐘同步機制,待測設計(DUT)與參考模型之間可能出現時序不同步的問題,影響驗證準確性。更關鍵的是,RVVI在系統級建模方面存在不足,無法為包含操作系統啟動、設備初始化及外設交互在內的全芯片級(SoC)場景提供有效支持。

此外,當設計包含自定義擴展指令時,為兼容RVVI標準所需的基礎設施改造不僅帶來額外維護負擔,還可能引入新的驗證漏洞。這些因素共同限制了RVVI在純仿真環境中處理復雜SoC工作負載的能力。

3.解決方案:基于事務級的加速(TBA)

面對RISC-V處理器在驗證效率、設計規模及系統復雜度方面的多重挑戰,基于事務級的加速(Transaction-Based Acceleration, TBA)已成為應對這些問題的關鍵解決方案。TBA通過提高驗證抽象層級,突破傳統周期精確仿真的性能限制,顯著提升驗證吞吐量,尤其適用于當前日益復雜的SoC及支持自定義擴展的RISC-V設計。

TBA采用事務級建模(Transaction-Level Modeling, TLM)接口與專用通信協議,建立起軟件測試環境與硬件設計之間的高效協作機制。與傳統的逐周期信號交互方式不同,TBA將諸如DMA傳輸、存儲器讀寫等多周期操作封裝為完整事務,在更高抽象層級完成數據交換。這種方式極大減少了軟硬件間所需傳輸和處理的數據量,測試平臺通過總線功能模型(BFM)以事務為單位與硬件進行通信,在提升效率的同時也降低了驗證環境的整體復雜度。

在體系架構層面,TBA明確劃分了軟硬件驗證功能:硬件側集成了可綜合的HDL設計,包括被測設計(DUT)、總線功能模型(BFM)以及時鐘與復位生成模塊;軟件側則承載非時序相關的測試任務,包括測試控制、激勵生成、參考模型、檢查機制及覆蓋率收集。這種分區策略充分發揮硬件執行高速性與軟件靈活性的雙重優勢,為構建高效系統級驗證環境奠定基礎。

TBA不僅在高吞吐量并行執行方面表現優異,還具備多方面的顯著優勢:

·驗證速度大幅提升:TBA可實現較傳統RTL仿真10–1000倍的加速效果。其多時鐘周期事務處理機制避免了逐周期仿真開銷,顯著縮短驗證周期,加快產品上市時間(Time-to-Market, TTM),并支持更高效的回歸測試

·早期軟件開發與驗證:TBA支持軟硬件協同開發,軟件團隊可在流片前進行驅動和固件驗證,大幅縮短系統集成時間,降低項目風險

·卓越的可擴展性:TBA能夠高效處理超大規模SoC和ASIC設計驗證,克服了傳統RTL仿真在規模和性能方面的局限性

·調試與驗證效率提升:TBA支持事務級調試,無需追蹤大量信號和周期,極大簡化錯誤定位過程。內置協議檢查器可自動檢測違規操作,參考模型能夠與實際RTL輸出進行實時比對,確保設計符合預期。軟件端覆蓋率收集與分析功能更全面保障驗證完備性

TBA不僅在特定驗證場景中表現突出,更在通用驗證環境中展現出廣泛的應用價值。其通過重構驗證效率邊界,為現代復雜芯片設計提供了關鍵的技術支撐,已成為驗證流程中不可或缺的重要組成部分。

4.基于事務級的加速(TBA) 在 RVVI 中的應用

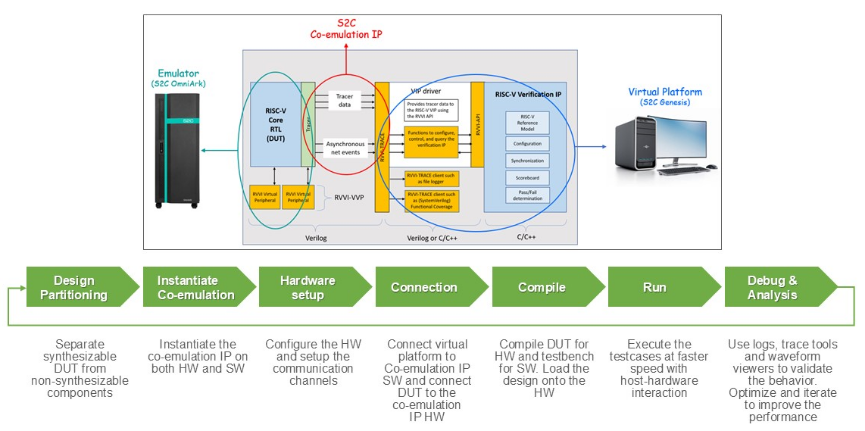

為充分發揮事務級加速(TBA)在RISC-V驗證中的效能,其與RISC-V驗證接口(RVVI)的高效集成尤為關鍵。該集成方案通過系統級協同仿真架構,在保持RVVI規范要求的周期精度的同時,大幅提升驗證效率與系統可擴展性。

在實際應用中,該系統采用分區的測試平臺架構:虛擬平臺負責運行參考模型、RVVI檢查器及覆蓋率收集模塊,而RISC-V核心則部署于仿真加速平臺(如思爾芯的芯神匠架構設計軟件和芯神鼎硬件仿真系統)中運行。這種架構既保留了軟件環境的靈活性與可調試性,也充分利用了硬件仿真平臺的高速執行能力。

為實現跨平臺的高效協作,協同仿真IP利用TBA技術建立起穩定、高帶寬的通信信道。TBA的事務級抽象機制不僅有效降低了通信開銷,還確保了芯神鼎硬件仿真系統與芯神匠架構設計虛擬平臺間的精確同步,從而在分布式系統中維持嚴格的時間精度與一致性。該通信層能夠可靠地傳輸RVVI所需的指令執行軌跡、內存訪問記錄等關鍵跟蹤信息,確保在指令集仿真器(ISS)與硬件仿真系統之間實現無縫的狀態比對與行為驗證。

通過TBA與RVVI的深度融合,驗證團隊能夠在享受事務級加速帶來的性能提升的同時,繼續遵循標準化的驗證接口與流程。這不僅顯著加速了復雜驗證場景的運行,如操作系統啟動、多核同步及異常處理測試,也為具有自定義擴展的RISC-V處理器提供了高效且可重用的驗證解決方案。

圖2TBA+RVVI流程

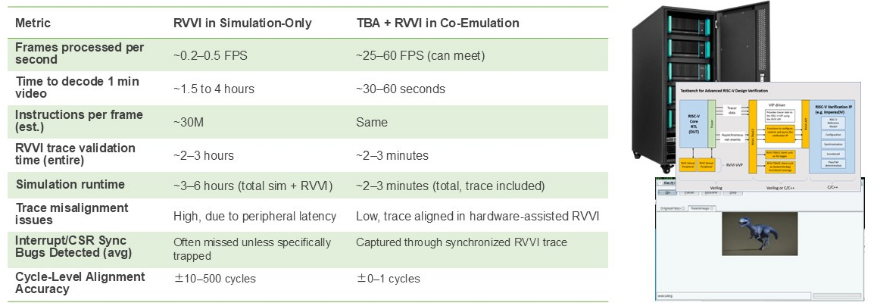

通過在視頻處理(分辨率:320×180)用例中的實際驗證,基于TBA與RVVI的協同仿真架構展現出顯著成效。測試結果顯示,該方案在維持RVVI周期精度的同時,實現了較傳統仿真方法25倍以上的加速效果。視頻處理流水線中的幀緩存管理、像素運算及數據傳輸等關鍵操作均得到充分驗證,其處理吞吐量完全滿足實時性要求。

值得注意的是,在此類數據密集型應用中,TBA通信信道的高帶寬與低延遲特性有效避免了仿真瓶頸,確保了視頻幀處理的連貫性與完整性。同時,RVVI接口成功捕獲到所有自定義指令的執行軌跡,驗證了其在實際應用場景中的兼容性與可靠性。覆蓋率分析表明,功能覆蓋率達到98.5%,有效保證了驗證的完備性。

圖3 視頻處理(分辨率:320×180)用例

這一結果充分證明了TBA與RVVI相結合的方案在處理具有高數據吞吐需求的復雜SoC設計中的實用價值,為同類多媒體處理芯片的驗證提供了高效、可靠的解決方案。

增值稅法實施條例向社會征求意見,有哪些看點?

漢陰縣實驗小學太平校區:會演展才藝 游園樂童年

夜間上門指導除隱患,珠海消防:這些用火雷區別踩

《女神異聞錄5皇家版》秋季特賣新史低93.8

馬琳大逆轉 10連勝背靠背奪冠

6名中國金花進入中網女單第二輪 袁悅收獲生日大禮包

實木家具這樣搭,美翻了

艾爾登法環什么類型武器好用一點

青年培養 “接地氣” 賦能發展 “加速度” ——義縣供電分公司圓滿完成2025年崗位“助理制”考核評價工作

珠海原創話劇《龍騰伶仃洋》,走進杭州灣大橋!

正榮地產擬發行2.2億美元優先票據 年息5.89%

Tao家集:寓情于家,自得其樂

濃眉哥狂砍45+10完爆唐斯 鵜鶘勝森林狼取4連勝

督導垃圾分類及“十五運”服務保障工作,珠海城管這樣做→

江海建設集團領導與湖北省武漢市蔡甸區常務副區長會談

Copyright © 2017-now 國際動態傳媒 版權所有